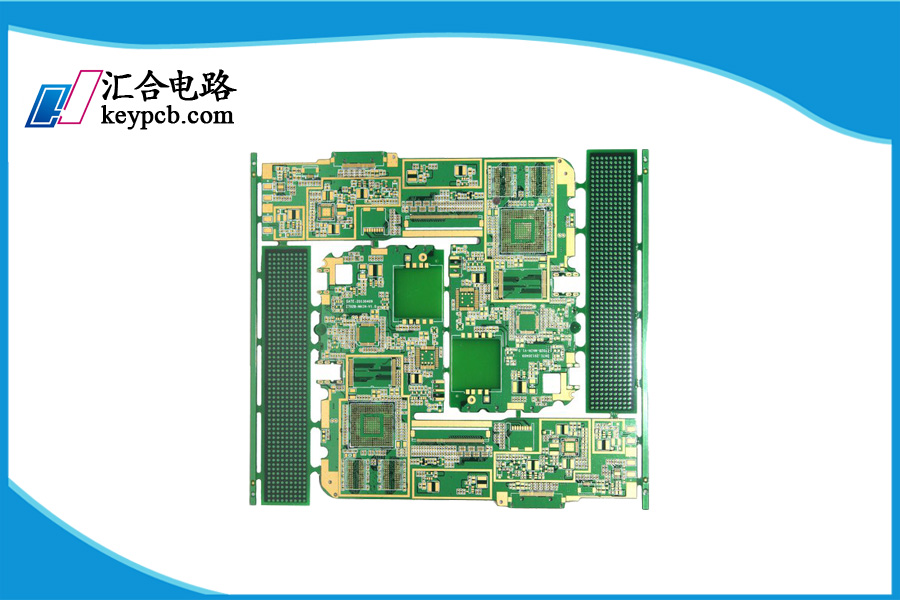

由于越来越多的ADC采用了差分输入结构,所以差分驱动器已成为ADC驱动必要的器件。目前,有众多技术可以将宽频带双运算放大器应用于差分ADC驱动器。理论上,差分结构可以消除二次谐波失真。实际上,只有精心布局的pcb快速打样能够有效地抑制二次谐波失真。采用对称设计,可以通过差分反相配置来使放大器获得最好的转换速率。

为了使差分结构对于二次谐波失真的消减能力达到最佳,必须对pcb快速打样的板层数、特征阻抗、元件位置、地线层、对称性、电源去耦合及其他许多方面进行优化,这些在设计PCB时都需要被考虑到。

pcb快速打样采用对称设计,需要考虑元件对称性和信号路径对称性。元件对称性是指所有的板上元件都按照特定的模式排列。信号路径对称性是指更注重的是信号路径的对称性而不是元件布局上的对称砂。

一个采用运算放大器OPA695构成的差分驱动器与ADS55OO ADC的接口电路,考虑元件对称性的pcb快速打样设计。对称中线被定义为穿过变压器(Tin)中央的直线。输出电阻Routa和Route基于对称中线等距分布。尽管这种布局看上去使人赏心悦目,但仔细分析,可以看到它仍然对放大器引脚输出的信号路径产生了一定的影响。例如,在SOIC-8封装的运算放大器中,输出引脚通常在引脚端6,因此,UA的引脚端6到中心的距离与UB的不同。这种差异必须通过加长某一信号路径的方式来补偿。

相关阅读:数字集成电路板制作模拟方法【汇合】